# МИНИСТЕРСТВО НАУКИ И ВЫСШЕГО ОБРАЗОВАНИЯ РОССИЙСКОЙ ФЕДЕРАЦИИ Федеральное государственное автономное образовательное учреждение высшего образования «Национальный исследовательский ядерный университет « МИФИ »

#### Снежинский физико-технический институт-

филиал федерального государственного автономного образовательного учреждения высшего образования «Национальный исследовательский ядерный университет « МИФИ »

(СФТИ НИЯУ МИФИ)

Кафедра: <u>АИиВС</u> (наименование кафедры)

#### ОТЧЕТ ПО КУРСОВОМУ ПРОЕКТУ

по курсу <u>Теория автоматов</u> (наименование учебной дисциплины)

на тему «Синтез цифровых управляющих автоматов»

| Студент       | <i>Группа</i> : ПАС-30Д<br>Домрачева Ю.К |

|---------------|------------------------------------------|

| Студент       | Горшкова А.К.                            |

| Преподаватель | Крушный В.В.                             |

Снежинск 2022 г.

## Содержание

| Введение                                                                             | 3  |

|--------------------------------------------------------------------------------------|----|

| 1 Канонический метод структурного синтеза                                            | 4  |

| 2 Синтез цифрового автомата по граф-схеме алгоритма                                  | 8  |

| 2.2 Отмеченная ГСА                                                                   | 10 |

| 2.3 Структурный синтез автомата                                                      | 12 |

| 3 Синтез автомата с программируемой логикой                                          | 14 |

| 3.1 Адресация микрокоманд с двумя принудительными адресами                           | 14 |

| 3.2 Адресация микрокоманд с одним принудительным адресом (инкремент текущего адреса) | 16 |

| 3.3 Адресация микрокоманд с одним принудительным адресом (инкремент адреса перехода) | 18 |

| 3.4 Естественная адресация                                                           | 20 |

| Заключение                                                                           | 23 |

| Список литературы                                                                    | 24 |

#### Введение

Данная курсовая работа состоит из трёх разделов. В первом разделе представлен синтез цифрового автомата по каноническому методу структурного синтеза. Результатом этого метода является система логических уравнений и комбинационная логическая схема, реализующих данную систему.

Структурный синтез цифрового автомата выполнен на основании заданных таблицы переходов и таблицы выходов. Для того чтобы реализовать автомат по данному методу выполнено следующее:

- 1) структуризация входов, выходов и состояний автомата;

- 2) кодировка входных, выходных сигналов и внутренних состояний автомата;

- 3) получение кодированных таблиц переходов и выходов структурного автомата;

- 4) получение логических функций по кодированным таблицам;

- 5) построение функционально-логической схемы автомата на основании полученных в результате синтеза логических функций.

Во втором разделе представлен цифровой автомат по ГСА, выполнен структурный синтез автомата.

В третьем разделе представлен синтез автомата с жёсткой и программируемой логикой по трем видам адресации.

#### 1 Канонический метод структурного синтеза

Выполнен структурный синтез частичного автомата А, заданного своими таблицами переходов и выходов, представленных в таблице 1.1 и таблице 1.2.

Таблица 1.1 – Таблица переходов

Таблица 1. 2 – Таблица выходов

| δ              | $a_1$          | $a_2$ | $a_3$ | a <sub>4</sub> |

|----------------|----------------|-------|-------|----------------|

| $\mathbf{Z}_1$ | $\mathbf{a}_3$ | -     | $a_2$ | $a_1$          |

| $\mathbf{Z}_2$ | -              | $a_2$ | $a_4$ | -              |

| <b>Z</b> 3     | $a_2$          | $a_3$ | -     | $a_3$          |

| λ              | $a_1$          | $a_2$      | $a_3$                 | $a_4$      |

|----------------|----------------|------------|-----------------------|------------|

| $\mathbf{Z}_1$ | $\mathbf{W}_1$ | -          | W <sub>2</sub>        | <b>W</b> 3 |

| $\mathbf{Z}_2$ | ı              | $W_2$      | <b>W</b> <sub>3</sub> | -          |

| <b>Z</b> 3     | <b>W</b> 2     | <b>W</b> 3 | -                     | <b>W</b> 3 |

В качестве элементов памяти используется Т –триггер.

Произведена кодировка входных, выходных сигналов и внутренних состояний автомата. Количество входных абстрактных сигналов F=3, количество входных структурных сигналов  $n=\log_2 F=\log_2 F=1$   $\log_2 F=1$ , то есть  $X=\{x1, x2\}$ . Количество выходных абстрактных сигналов G=3, количество выходных структурных сигналов G=3, количество выходных структурных сигналов G=3, количество выходных структурных сигналов G=3, количество внутренних состояний абстрактного автомата G=3, количество двоичных элементов памяти (триггеров) G=30 G=31 G=32.

Кодирование входных, выходных сигналов и внутренних состояний представлено в таблицах 1.3 -1.5.

Таблица 1.3 — Кодирование входных сигналов

| Z              | $\mathbf{x}_1$ | <b>X</b> 2 |

|----------------|----------------|------------|

| $\mathbf{Z}_1$ | 0              | 0          |

| $\mathbf{Z}_2$ | 0              | 1          |

| $\mathbf{Z}_3$ | 1              | 0          |

Таблица 1.4 – Кодирование выходных сигналов

| W              | <b>y</b> <sub>1</sub> | <b>y</b> <sub>2</sub> |

|----------------|-----------------------|-----------------------|

| $\mathbf{W}_1$ | 0                     | 0                     |

| $\mathbf{w}_2$ | 0                     | 1                     |

| $\mathbf{W}_3$ | 1                     | 0                     |

Таблица 1.5 – Кодирование выхолных сигналов

| A     | $Q_1$ | $Q_2$ |

|-------|-------|-------|

| $a_1$ | 0     | 0     |

| $a_2$ | 0     | 1     |

| $a_3$ | 1     | 0     |

| $a_4$ | 1     | 1     |

Кодированные таблицы переходов и выходов структурного автомата представлены на таблицах 1.3-1.5. В таблицах переходов и выходов исходного абстрактного автомата  $z_i$ ,  $w_i$ , a, i заменены соответствующие коды. Кодированные таблицы переходов и выходов представлены в таблицах 1.6 и 1.7.

|       |                   | $a_1$ | $a_2$ | $a_3$ | $a_4$ |

|-------|-------------------|-------|-------|-------|-------|

|       | $Q_1Q_2$ $x_1x_2$ | 00    | 01    | 10    | 11    |

| $z_1$ | 00                | 10    | ı     | 01    | 00    |

| $z_2$ | 01                | ľ     | 01    | 11    | -     |

| $z_3$ | 10                | 01    | 10    | -     | 10    |

|                |                   | $a_1$ | $a_2$ | $a_3$ | $a_4$ |

|----------------|-------------------|-------|-------|-------|-------|

|                | $Q_1Q_2$ $x_1x_2$ | 00    | 01    | 10    | 11    |

| z <sub>1</sub> | 00                | 00    | -     | 01    | 10    |

| Z <sub>2</sub> | 01                | ı     | 01    | 10    | ı     |

| <b>Z</b> 3     | 10                | 01    | 10    | -     | 00    |

В кодированной таблице переходов заданы функции:

$$Q_1^{t+1} = \square_1(x_1, x_2, Q_1^t, Q_2^t),$$

$$Q_2^{t+1} = \square_2(x_1, x_2, Q_1^t, Q_2^t).$$

В кодированной таблице выходов заданы функции:

$$y_1 = \phi_1(x_1, x_2, Q_1^t, Q_2^t), y_2 = \phi_2(x_1, x_2, Q_1^t, Q_2^t).$$

При каноническом методе синтез сведен к получению функций:

$$y_1 = \phi_1(x_1, x_2, Q_1, Q_2);$$

$$y_2 = \phi_2(x_1, x_2, Q_1, Q_2);$$

$$T_1 = f_1(x_1, x_2, Q_1, Q_2);$$

$$T_2 = f_2(x_1, x_2, Q_1, Q_2).$$

Функции  $y_1$  и  $y_2$  получены из кодированной таблицы выходов.

Карты Карно для минимизации выражения для  $y_1$  и  $y_2$  изображены на рисунке 1.1.

|    | 00 | 01 | 11 | 10 |

|----|----|----|----|----|

| 00 |    | -  | 1  |    |

| 01 | -  |    | -  | 1  |

| 11 | -  | -  | -  | -  |

| 10 |    | 1  |    | 1  |

| xì | <del>Q1 Q2</del> | 00 |          | 01 | 11 |   | 10 |  |

|----|------------------|----|----------|----|----|---|----|--|

| F  | 00               |    |          | -  |    |   | 1  |  |

|    | 01               | -  |          | 1  | -  |   |    |  |

|    | 11               | -  |          | -  | -  |   | -  |  |

|    | 10               | 1  | <u> </u> |    |    | + | -  |  |

a б Рисунок 1.1 – Карты Карно для  $y_1\left(a\right)$  и  $y_2\left(\delta\right)$  Результат минимизации представлен в выражении (1):

С помощью таблицы функций возбуждения (Таблица 1.8) выведены выражения для Т1 и Т2. Используя код исходного состояния автомата и код состояния перехода на основании таблицы входов триггера, найдено требуемое возбуждения, представленное функций выражение рисунке обеспечивающее заданный переход.

Тоблицо 1 9 Тоблицо функций возбужности

| Табли                                 | ца 1.8 | 8 – Ta             | блица (   | рункц | ИЙ :     | возб | ужде               | кин      |                       |     |   |

|---------------------------------------|--------|--------------------|-----------|-------|----------|------|--------------------|----------|-----------------------|-----|---|

| Q1Q2<br>X <sub>1</sub> X <sub>2</sub> | 00     | 01                 | 10        | 11    |          |      |                    |          |                       |     |   |

| 00                                    | 10     | -                  | 11        | 11    | -        |      |                    |          |                       |     |   |

| 01                                    | -      | 00                 | 01        | -     |          |      |                    |          |                       |     |   |

| 10                                    | 01     | 11                 | -         | 01    |          |      |                    |          |                       |     |   |

|                                       |        |                    | ←<br>T1T2 |       | _        | Q1Q2 |                    |          |                       |     |   |

| Q1Q2                                  | 00     | 01                 |           |       |          |      | 00                 | 01       | 11                    | 10  |   |

| $x_1x_2$                              | 00     | 01                 | 11 10     |       | $x_1x_2$ | 00   |                    | t -      | 1                     | 1   |   |

| 00                                    | 1      | -                  | 1 1       |       |          |      |                    | <u> </u> | /                     | 1   |   |

| 01                                    | Рису   | <del>/нок  1</del> | .2 - Ka   | рты К | арн      | ОДЛ  | я T <sub>1</sub> ( | а) и '   | $\Gamma_2$ ( $\delta$ | 1   |   |

|                                       | - (    | $\rightarrow$      |           |       |          | 11   | _                  | _        | -                     | -   |   |

| 11                                    | -      | -   -              | -  -      |       |          | 10   | / 1                | (a)      | 1                     | +   |   |

| 10                                    |        | $1 \parallel$      |           | _     |          | 10   | / 1                | g        | 1                     |     |   |

|                                       |        | ال                 |           |       |          |      |                    | ı        |                       | الح | l |

|                                       |        | a                  |           |       |          |      |                    |          |                       |     |   |

| T _                                   | ~ ~    | V/v                | o ō 2     | 2     |          |      |                    |          |                       |     |   |

$$T_1 = \bar{x}_1 \bar{x}_2 \, \forall x_1 \, Q_1 \bar{Q}_2^{2} \tag{2}$$

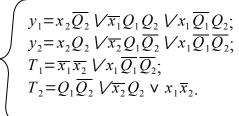

На основании полученных в результате синтеза булевых выражений (1), (2) построена функционально-логическая схема автомата, изображённая на рисунке 1.3.

Для этого уравнения 1 и 2 представлены в виде:

Рисунок 1.3 – Функционально-логическая схема автомата

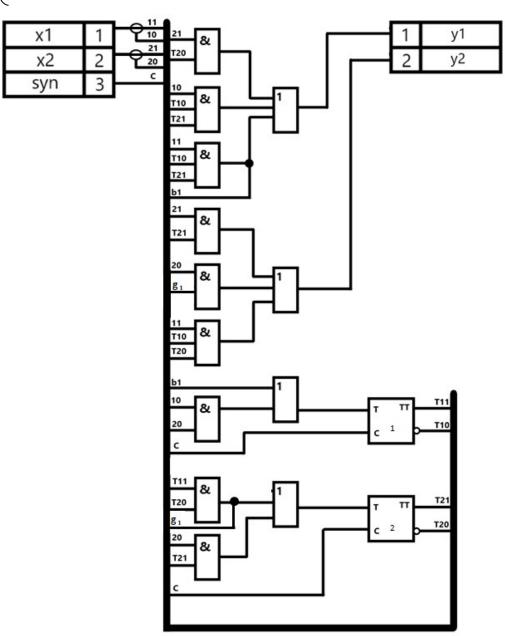

#### 2 Синтез цифрового автомата по граф-схеме алгоритма

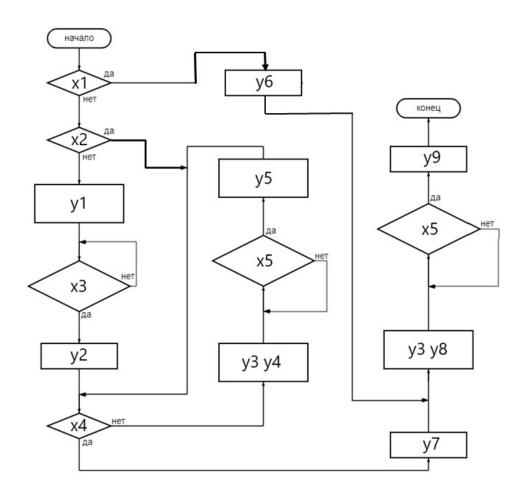

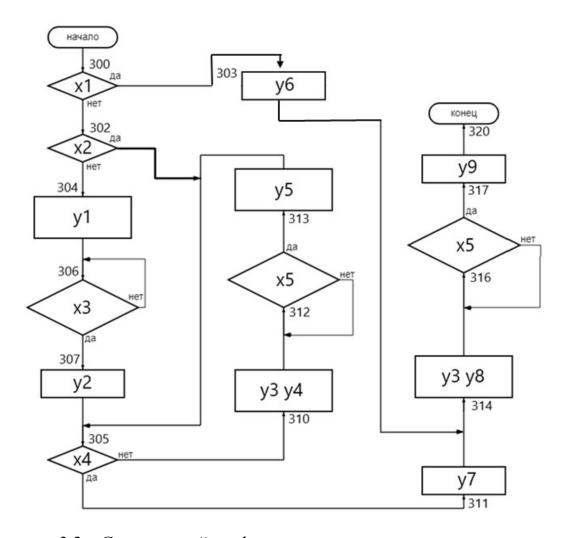

Рисунок 2.1 – Алгоритм функционирования

Синтез микропрограммного автомата по граф — схеме алгоритма, приведенный на рисунке 2 .1, осуществлён в два этапа:

- 1) получение отмеченной ГСА;

- 2) построение графа автомата в виде списковых структур (таблицы переходов).

## 2.1 Кодированная ГСА

Таблица 2.1 – Кодирование логических выражений

|                      | Выражение             | Код выражения |

|----------------------|-----------------------|---------------|

| w=0                  | <b>X</b> <sub>1</sub> | 1             |

| j=0                  | X <sub>2</sub>        | 2             |

| АУ завершило работу? | X <sub>3</sub>        | 3             |

| $\Pi A = 01$         | X <sub>4</sub>        | 4             |

| П завершила работу?  | <b>X</b> 5            | 5             |

Таблица 2.2 – Кодирование управляющих сигналов

|              | Сигнал                | Код сигнала |

|--------------|-----------------------|-------------|

| Р1АУ:=ИР     |                       |             |

| Р2АУ:=РАРК   | y <sub>1</sub>        | 01          |

| РКОАУ:=Сл    |                       |             |

| РАРК:=РВАУ   | y <sub>2</sub>        | 02          |

| РАП:=РАРК    | <b>y</b> <sub>3</sub> | 03          |

| РКОП:=Вб     | V.                    | 04          |

| И3->П        | У4                    | 04          |

| РАРК:=(РВП)а | V-                    | 05          |

| ПА:=(РВП)па  | <b>y</b> 5            | 03          |

| СК:=СК+1     | y <sub>6</sub>        | 06          |

| СК:=РАРК     | <b>y</b> <sub>7</sub> | 07          |

| РАП:=СК      | y <sub>8</sub>        | 10          |

| РК:=РВП      | <b>y</b> 9            | 11          |

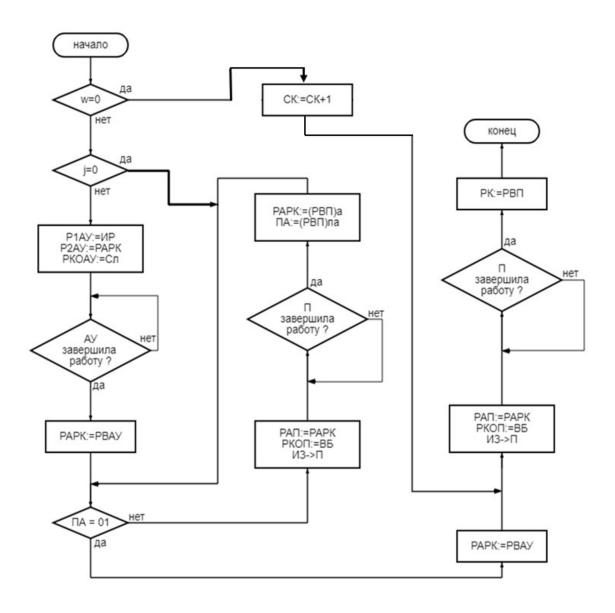

На рисунке 2.2 представлена полученная кодированная граф-схема алгоритма.

Рисунок 2.2 - Кодированная ГСА

#### 2.2 Отмеченная ГСА

На этапе получения отмеченной ГСА входы вершин отмечены символами  $a_1,\,a_2,\,\dots$  ,  $a_H$  по следующим правилам:

- 1) символом  $a_1$  обозначен вход вершины, следующий за начальной, а также вход конечной вершины;

- 2) символами  $a_2, \ldots, a_H$  обозначаются входы всех вершин, следующих за операторными;

- 3) если вход вершины обозначен, то только одним символом;

- 4) входы различных вершин, за исключением конечного, обозначаются различными символами.

Таким образом, отмеченная ГСА представлена на рисунке 2. 3.

Рисунок 2.3 – Отмеченная ГСА

#### 2.3 Структурный синтез автомата

Кодирование состояний автомата приведено в таблице 2.3.

Таблица 2.3 – Кодирование состояний

|   | 00    | 01    | 10    | 11    |

|---|-------|-------|-------|-------|

| 0 | $a_I$ | $a_2$ | $a_3$ | $a_4$ |

| 1 | $a_5$ | $a_6$ |       |       |

Из таблицы переходов следует, что в автомате количество состояний M=6, таким образом число элементов памяти составляет:  $m=\log_2 M = \log_2 6 = 3$ .

Для синтеза использованы D триггеры.

С использованием отмеченной ГСА построена обратная структурная таблица, представленная в таблице 2.4, в которой сначала записываются все переходы в первое состояние, затем во второе и т.д.

В первом столбце указываются все состояния  $a_m$ , из которых осуществляются переходы. Коды этих состояний  $K(a_m)$  после кодирования занесены во второй столбец. В третьем и четвёртом столбцах записаны состояния  $a_s$ , в которых произошли переходы, и их коды  $K(a_s)$ . Пятый и шестой столбцы содержат входные  $X(a_r,a_s)$  и выходные сигналы  $Y(a_m,a_s)$ , входящие в пути перехода. В седьмом столбце таблицы перечислены обязательные функции возбуждения  $\Psi(a_m,a_s)$ , вырабатываемые на соответствующих переходах для D-триггера и в восьмом - номер пути перехода для удобства идентификации.

Таблица 2.4 – Обратная структурная таблица

| $a_m$   | $K(a_m)$ | $a_s$                 | $K(a_s)$ | $X(a_m, a_s)$                       | $Y(a_m, a_s)$                               | $\Psi(a_m, a_s)$ | P  |                              |

|---------|----------|-----------------------|----------|-------------------------------------|---------------------------------------------|------------------|----|------------------------------|

| $a_6$   | 101      | $a_1$                 | 000      | $x_5$                               | <i>y</i> <sub>9</sub>                       | -                | 1  | $\left.\right\} \Phi(a_{l})$ |

| $a_I$   | 000      | $a_2$                 | 001      | $\overline{x}_1 \overline{x}_2$     | $y_1$                                       | $D_I$            | 2  |                              |

| $a_2$   | 001      | $a_2$                 | 001      | $\overline{x_3}$                    | -                                           | $D_I$            | 3  | $\int \Phi(a_2)$             |

| $a_2$   | 001      | $a_3$                 | 010      | $x_3$                               | $y_2$                                       | $D_2$            | 4  | $\Phi(a_3)$                  |

| $a_4$   | 011      | $a_3$                 | 011      | $x_5$                               | $y_5$                                       | $D_2$            | 5  |                              |

| $a_{l}$ | 011      | <i>a</i> <sub>4</sub> | 011      | $\overline{x_1} x_2 \overline{x_4}$ | <i>y</i> <sub>3</sub> <i>y</i> <sub>4</sub> | $D_1 D_2$        | 6  |                              |

| $a_3$   | 010      | $a_4$                 | 011      | $\overline{x}_4$                    | <i>y</i> <sub>3</sub> <i>y</i> <sub>4</sub> | $D_1 D_2$        | 7  | $\Phi(a_4)$                  |

| $a_4$   | 011      | $a_4$                 | 011      | $\overline{X_5}$                    | -                                           | $D_1 D_2$        | 8  |                              |

| $a_{I}$ | 000      | $a_5$                 | 100      | $x_1$                               | <i>y</i> <sub>6</sub>                       | $D_3$            | 9  |                              |

| $a_{I}$ | 000      | $a_5$                 | 100      | $\overline{x_1}x_2x_4$              | <i>y</i> <sub>7</sub>                       | $D_3$            | 10 | $\Phi(a_5)$                  |

| $a_3$   | 010      | $a_5$                 | 100      | $x_4$                               | <i>y</i> <sub>7</sub>                       | $D_3$            | 11 |                              |

| $a_5$   | 100      | $a_6$                 | 101      | 1                                   | <i>y</i> <sub>3</sub> <i>y</i> <sub>8</sub> | $D_1 D_3$        | 12 | $\int \Phi(a_6)$             |

| $a_6$   | 101      | $a_6$                 | 101      | $\overline{x}_5$                    | _                                           | $D_1 D_3$        | 13 |                              |

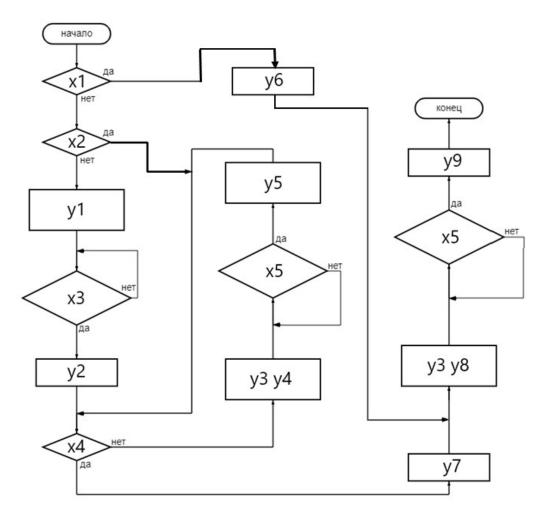

### 2.4 Функционально-логическая схема автомата

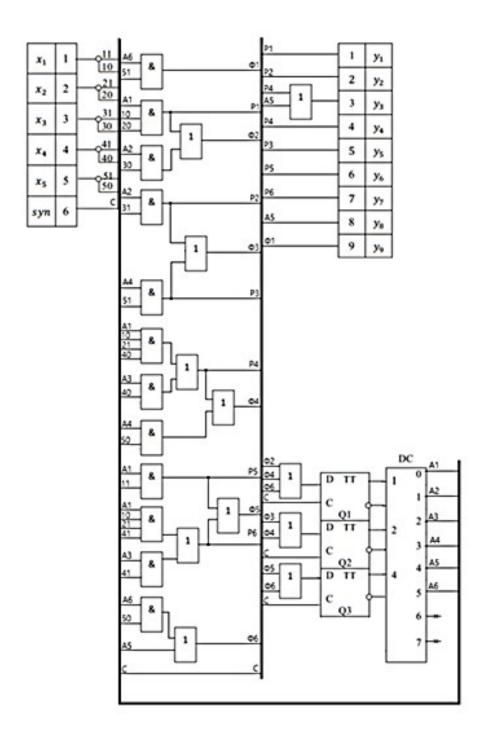

На основании полученной обратной структурной таблицы получается функционально-логическая схема автомата, изображенная на рисунке 2.4.

Рисунок 2.4 – Функционально-логическая схема автомата

#### 3 Синтез автомата с программируемой логикой

#### 3.1 Адресация микрокоманд с двумя принудительными адресами

Для того, чтобы реализовать цифровой автомат с программируемой логикой с двумя принудительными адресами, составлен набор микрокоманд. Структура каждой микрокоманды включает в себя: микрооперации, выполняемые за один такт, код проверяемого логического условия и два адреса следующих микрокоманд. Адрес следующей микрокоманды определен в зависимости от кода логического условия КЛУ и значения соответствующего логического условия х<sub>i</sub>, либо полем A1, либо полем A2.

Кодировка микропрограммы выполнена в восьмеричной системе счисления. Набор микрокоманд представлен в таблице 3.1.

Длина микрокоманды составила N=33 бит (11 символов  $\times$  3бита). Объём занимаемой ёмкости постоянной памяти при данном способе адресации микрокоманд составил E=495 бит (15 микрокоманд  $\times$  33 бит).

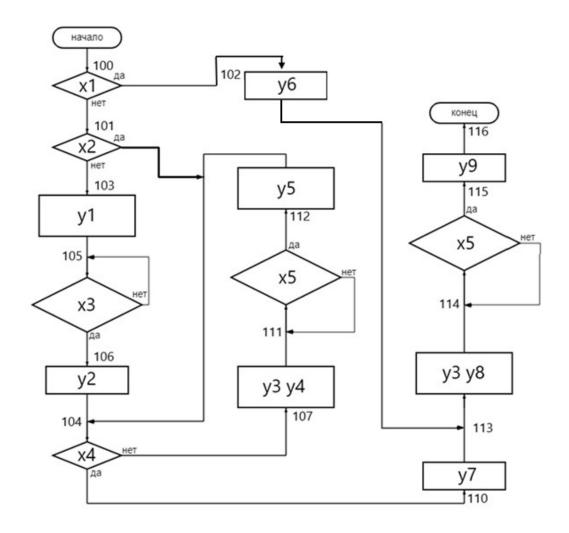

Пример формирования микропрограммы с двумя принудительными адресами представлен на рисунке 3.1.

Рисунок 3.1 – Граф структура микропрограммы с двумя принудительными адресами

Таблица 3.1 – Набор микрокоманд

| $A_{T}$ | $Y_1$ | $Y_2$ | КЛУ | $A_1$ | $A_2$ |

|---------|-------|-------|-----|-------|-------|

| 100     | 00    | 00    | 1   | 101   | 102   |

| 101     | 00    | 00    | 2   | 103   | 104   |

| 102     | 06    | 00    | 0   | 113   | 000   |

| 103     | 01    | 00    | 3   | 105   | 106   |

| 104     | 00    | 00    | 4   | 107   | 110   |

| 105     | 00    | 00    | 3   | 105   | 106   |

| 106     | 02    | 00    | 4   | 107   | 110   |

| 107     | 03    | 04    | 5   | 111   | 112   |

| 110     | 07    | 00    | 0   | 113   | 000   |

| 111     | 00    | 00    | 5   | 111   | 112   |

| 112     | 05    | 00    | 4   | 107   | 110   |

| 113     | 03    | 10    | 5   | 114   | 115   |

| 114     | 00    | 00    | 5   | 114   | 115   |

| 115     | 11    | 00    | 0   | 116   | 000   |

| 116     | 77    | 00    | 0   | 000   | 000   |

stop

3.2 Адресация микрокоманд с одним принудительным адресом (инкремент текущего адреса)

При данном способе адресации для формирования адреса следующей микрокоманды отводится единственное поле адреса перехода Ар.

Если поле КЛУ=0, то значение Ар, безусловно, определяет адрес следующей микрокоманды. Если поле кода логического условия не нулевое, то адрес следующей микрокоманды реализуется условным переходом: если значение проверяемого логического условия  $x_i$ =0, то РАПП:=Ар, если  $x_i$ =1, то второй адрес перехода определяется инкрементом адреса текущей микрокоманды, хранящегося в регистре адреса постоянной памяти с функцией инкрементного счётчика (AT +1).

Длина микрокоманды составила N=24 бит. Объём занимаемой ёмкости постоянной памяти при данном способе адресации микрокоманд составил E=480 бит.

Набор микрокоманд представлен в таблице 3.2.

Пример формирования микропрограммы с одним принудительным адресом показан на рисунке 3.2 .

Рисунок 3.2 – Структурный граф микропрограммы с одним принудительным адресом (инкремент текущего адреса)

Таблица 3.2 – Набор микрокоманд

| 1    |       |     |       |                |                           |

|------|-------|-----|-------|----------------|---------------------------|

|      | $A_p$ | КЛУ | $Y_2$ | $\mathbf{Y}_1$ | $\mathbf{A}_{\mathrm{T}}$ |

|      | 202   | 1   | 00    | 00             | 200                       |

|      | 202   | 0   | 00    | 06             | 201                       |

|      | 222   | 5   | 10    | 03             | 202                       |

|      | 204   | 0   | 00    | 11             | 203                       |

| stop | 000   | 0   | 00    | 77             | 204                       |

|      | 210   | 2   | 00    | 00             | 205                       |

|      | 215   | 4   | 00    | 00             | 206                       |

| jump | 202   | 0   | 00    | 07             | 207                       |

|      | 213   | 3   | 00    | 01             | 210                       |

|      | 215   | 4   | 00    | 02             | 211                       |

| jump | 207   | 0   | 00    | 00             | 212                       |

|      | 213   | 3   | 00    | 00             | 213                       |

| jump | 211   | 0   | 00    | 00             | 214                       |

|      | 220   | 5   | 04    | 03             | 215                       |

|      | 215   | 4   | 00    | 05             | 216                       |

|      | 207   | 0   | 00    | 00             | 217                       |

|      | 220   | 5   | 00    | 00             | 220                       |

| jump | 216   | 0   | 00    | 00             | 221                       |

|      | 222   | 5   | 00    | 00             | 222                       |

| jump | 203   | 0   | 00    | 00             | 223                       |

|      |       |     |       |                |                           |

3.3 Адресация микрокоманд с одним принудительным адресом (инкремент адреса перехода)

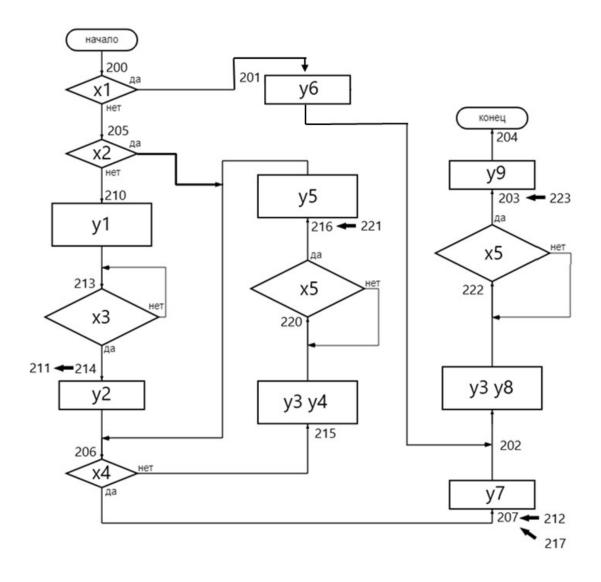

Адресация с инкрементом адреса перехода отличается от адресации с инкрементом текущего адреса лишь способом формирования адреса следующей микрокоманды при условном переходе. Если значение проверяемого логического условия  $x_i = 0$ , то РАПП := Ар, если  $x_i = 1$ , то второй адрес перехода определяется инкрементом адреса перехода Ар+1, записанного в регистре микрокоманды.

Длина микрокоманды составила N=23 бит. Объём занимаемой ёмкости постоянной памяти при данном способе адресации микрокоманд составил E=391 бит.

Набор микрокоманд представлен в таблице 3.3.

Пример формирования микропрограммы с одним принудительным адресом показан на рисунке 3.3.

Рисунок 3.3 – Структурный граф микропрограммы с одним принудительным выходом (инкримент адреса перехода)

Таблица 3.3 – Набор микрокоманд

| A <sub>T</sub> | $Y_1$ | $Y_2$ | КЛУ | $A_p$ |

|----------------|-------|-------|-----|-------|

| 300            | 00    | 00    | 1   | 302   |

| 301            | XX    | XX    | X   | XXX   |

| 302            | 00    | 00    | 2   | 304   |

| 303            | 06    | 00    | 0   | 314   |

| 304            | 01    | 00    | 0   | 306   |

| 305            | 00    | 00    | 4   | 310   |

| 306            | 00    | 00    | 3   | 306   |

| 307            | 02    | 00    | 4   | 310   |

| 310            | 03    | 04    | 5   | 312   |

| 311            | 07    | 00    | 0   | 314   |

| 312            | 00    | 00    | 5   | 312   |

| 313            | 05    | 00    | 4   | 310   |

| 314            | 03    | 10    | 5   | 316   |

| 315            | XX    | XX    | X   | XXX   |

| 316            | 00    | 00    | 5   | 316   |

| 317            | 11    | 00    | 0   | 320   |

| 320            | 77    | 00    | 0   | 000   |

stop

#### 3.4 Естественная адресация

В данном способе вводится два типа микрокоманд:

- 1) операторная микрокоманда, с признаком d=0;

- 2) условная микрокоманда, с признаком d=1.

Структура операторной микрокоманды: признак микрокоманды, микрооперации, выполняемые за один такт. Структура условной микрокоманды: признак микрокоманды, код проверяемого логического условия, адрес следующей микрокоманды.

При естественной адресации адрес следующей микрокоманды -  $A_T$  +1. При условном переходе, если проверяемое логическое условие  $x_i$ = 0, то следующей выполняется микрокоманда, адрес которой указан в адресном поле текущей микрокоманды; если  $x_i$  = 1, то следующей выполняется микрокоманда с инкрементом текущего адреса ( $A_T$  +1).

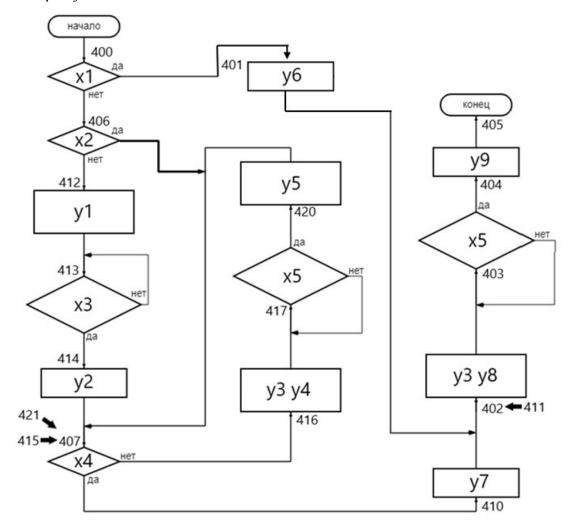

Для данного способа адресации длина микрокоманды составила N=16 бит, а объём занимаемой ёмкости постоянной памяти – E=288 бита.

Набор микрокоманд представлен в таблице 3.4.

Пример формирования микропрограммы с одним принудительным адресом показан на рисунке 3.4.

Рисунок 3.4 – Естественная адресация

Таблица 3.4 – Набор микрокоманд

| $A_T$ | d=0 | Y   |       |  |

|-------|-----|-----|-------|--|

|       | d=1 | КЛУ | $A_P$ |  |

| 400   | 1   | 1   | 406   |  |

| 401   | 0   | 0   | 006   |  |

| 402   | 0   | 3   | 010   |  |

| 403   | 1   | 5   | 403   |  |

| 404   | 0   | 0   | 011   |  |

| 405   | 0   | 7   | 000   |  |

| 406   | 1   | 2   | 412   |  |

| 407   | 1   | 4   | 416   |  |

| 410   | 0   | 0   | 007   |  |

| 411   | 1   | 0   | 402   |  |

| 412   | 0   | 0   | 001   |  |

| 413   | 1   | 3   | 413   |  |

| 414   | 0   | 0   | 002   |  |

| 415   | 1   | 0   | 407   |  |

| 416   | 1   | 0   | 004   |  |

| 417   | 1   | 5   | 417   |  |

| 420   | 0   | 0   | 005   |  |

| 421   | 1   | 0   | 407   |  |

stop

jump

jump

#### Заключение

#### В данной курсовой работе:

- 1) выполнен синтез цифрового автомата по каноническому методу структурного синтеза с построением функционально - логической схемы автомата;

- 2) Реализован цифровой синтез по ГСА с жесткой логикой. При реализации пользовались составленной обратной структурой таблицей переходов, по которой построена функционально логическая схема с использованием полной дешифрации состояний;

- Реализован синтез автомата с программируемой логикой тремя способами, наиболее оптимальной оказалась естественная адресация, т.к. объем занимаемой емкости памяти минимален E = 288 бит, но проигрывает по быстродействию

## Список литературы

- 1 Крушный В. В. Синтез цифровых управляющих автоматов: Учебное пособие. М.: НИЯУ МИФИ, 2011. 164 с.

- 2 ΓΟCT 2.105

- 3 Д.Э. Розенталь Русский язык. Грамматика.